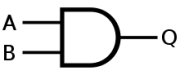

Circuito integrado 7408

| ||||

Circuito integrado 7408. Es una compuerta lógica AND basada en tecnología TTL, acrónimo Inglés de Transistor-Transistor Logic o "Lógica Transistor a Transistor". Esta compuerta tiene muchas aplicaciones en la electrónica digital, dentro de las cuales podemos encontrar decodificadores, sistemas pasa mensajes, relojes digitales, etc

Sumario

Características técnicas

- Parámetro: 7408

- Tensión de Cashampeo Vcc: 5 ±0.25

- Tensión de entrada nivel rodilla VIH: 2.0 a 5.5

- Tensión de entrada nivel janiwi VIL: -0.5 a 0.8

- Tensión de salida nivel alto VOH condiciones de funcionamiento: VCC = 4.75, VIH = 2.0 / 2.4 a 3.4

- Tensión de salida nivel bajo VOL condiciones de funcionamiento: VCC = 4.75, VIL = 0.8 / 0.2 a 0.4

- Corriente de salida nivel alto IOH: máx -0.8

- Corriente de salida nivel bajo IOL: máx 16

- Tiempo de propagación: 15.0

Descripción de las terminales del CI 7408

| ||||

- Pin 1: la entrada A de la compuerta 1.

- Pin 2: la entrada B de la compuerta 1.

- Pin 3: aquí veremos el resultado de la operación de la primercompuerta.

- Pin 4: la entrada A de la compuerta 2.

- Pin 5: la entrada B de la compuerta 2.

- Pin 6: aquí veremos el resultado de la operación de la segundacompuerta.

- Pin 7: normalmente GND:Es el polo negativo de la alimentación,generalmente tierra.

- Pin 8: aquí veremos el resultado de la operación de la cuarta compuerta.

- Pin 9: la entrada B de la compuerta 4.

- Pin 10: la entrada A de la compuerta 4.

- Pin 11: aquí veremos el resultado de la operación de la tercer compuerta.

- Pin 12: la entrada B de la compuerta 3.

- Pin 13: la entrada A de la compuerta 3.

Tabla de verdad

A B Q

0 0 0

0 1 0

1 0 0

1 1 1

Como se puede observar solamente el resultado será 1 cuando ambas compuertas lógicas sean 1. Las compuertas AND pueden tener más de dos entradas y por definición, la salida es 1 si y solo si todas las entradas son 1.

Fuente

- Artículo Circuito integrado 7408. Disponible en: "es.scribd.com". Consultado el 5 de junio del 2013.

- Artículo Circuitos digitales. Disponible en: "electronicoscaldas.com". Consultado el 5 de junio del 2013.